# A Dynamic Programming Model To Solve Optimisation Problems Using GPUs

#### Jonathan Francis O'Connell

School of Computer Science & Informatics

Cardiff University

A thesis submitted in partial fulfilment of the requirement for the degree of

Doctor of Philosophy

College of Physical Science and

Engineering January 2017

For my wife Emma, who made all this possible.

### **Declaration**

| This work has not previously been accepted in substance for any degree and is not being          |

|--------------------------------------------------------------------------------------------------|

| concurrently submitted in candidature for any degree.                                            |

|                                                                                                  |

| Signed (candidate)                                                                               |

| Date                                                                                             |

|                                                                                                  |

| Statement 1:                                                                                     |

| This thesis is the result of my own investigations, except where otherwise stated. Other         |

| sources are acknowledged by explicit references. A bibliography is appended.                     |

|                                                                                                  |

| Signed (candidate)                                                                               |

| Date                                                                                             |

|                                                                                                  |

| Statement 2:                                                                                     |

| I hereby give consent for my thesis, if accepted, to be available for photocopying and for       |

| inter-library loan, and for the title and summary to be made available to outside organisations. |

|                                                                                                  |

| Signed (candidate)                                                                               |

| Date                                                                                             |

#### Acknowledgements

Throughout the course of this PhD I've had the support of many people, all of which deserve an honourable mention here. Firstly, I must thank Christine Mumford, my long-suffering supervisor, whose invaluable support and advice have kept my research on track these last four or so years. I must mention the Cardiff University COMSC department for providing a superb working environment, a support network when work got tough, and a distraction during long days. Special thanks are due to Matt John who has been an office mate, flat mate, and good friend over the last few years. I would like to thank my supervisor at Bristol University, Elisabeth Oswald, for being so understanding and allowing me time to work on my thesis during my employment there as an RA. I must also thank my friends for keeping me sane during this process: Mads, Isaac, Rob, George, and James providing welcome relief from my work. The girls of Number 66, Abbi and Elin, deserve a special mention for enduring me far too many days a week, and providing me with unending hot beverages and food. The future in-laws, Mark and Valeria, for giving me a comfy sofa and home cooked dinners, and all the Findlay-Wilsons for looking after me so well. Finally, of course, I must thank my family – my Mum and Dad for providing me, often much-needed, emotional and financial support across the years; my brothers Jason, for giving me a cosy change of scenery every so often, and Christian, whose email to the head of school got me funding in my first year. To this day I have no idea what he said... Most of all, I must thank Emma. Without her encouragement, and steadfast belief in me, I would have never reached this point.

Without you all, this would have been impossible. Thank you.

#### **Abstract**

This thesis presents a parallel, dynamic programming based model which is deployed on the GPU of a system to accelerate the solving of optimisation problems. This is achieved by simultaneously running GPU based computations, and memory transactions, allowing computation to never pause, and overcoming the memory constraints of solving large problem instances. Due to this some optimisation problems, which are currently not solved in an exact manner for real world sized instances due to their complexity, are moved into the solvable realm. The model is implemented to solve, a range of different test problems, where artificially constructed test data is used to ensure good performance even in the worst cases. Through this extensive testing, we can be confident the model will perform well when used to solve real world test cases. Testing of the model was carried out using a range of different implementation parameters in relation to deployment on the GPU, in order to identify both optimal implementation parameters, and how the model will operate when running on different systems. All problems, when implemented in parallel using the model, show run-time improvements compared to the sequential implementations, in some instances up to hundreds of times faster, but more importantly also show high efficiency metrics for the utilisation of GPU resources. Throughout testing emphasis has been placed on GPU based metrics to ensure the wider generic applicability of the model. Finally, the parallel model allows for new problems to be defined through the use of a simple file format, enabling wider usage of the model.

# **Table of contents**

| Li | ist of figures |             |                                        |     |  |  |  |  |  |

|----|----------------|-------------|----------------------------------------|-----|--|--|--|--|--|

| Li | st of t        | ables       |                                        | xxi |  |  |  |  |  |

| 1  | Intr           | ntroduction |                                        |     |  |  |  |  |  |

|    | 1.1            | Introd      | uction                                 | 2   |  |  |  |  |  |

|    | 1.2            | Thesis      | Aims                                   | 4   |  |  |  |  |  |

|    | 1.3            | Contri      | butions                                | 5   |  |  |  |  |  |

|    | 1.4            | Thesis      | Structure                              | 6   |  |  |  |  |  |

|    | 1.5            | Public      | eations                                | 8   |  |  |  |  |  |

|    |                | 1.5.1       | Model Design                           | 8   |  |  |  |  |  |

|    |                | 1.5.2       | Implementation                         | 8   |  |  |  |  |  |

| 2  | Bac            | kgroun      | d                                      | 11  |  |  |  |  |  |

|    | 2.1            | Proble      | em Introduction                        | 13  |  |  |  |  |  |

|    |                | 2.1.1       | NP Complexity                          | 13  |  |  |  |  |  |

|    |                | 2.1.2       | The Longest Common Subsequence Problem | 15  |  |  |  |  |  |

|    |                | 2.1.3       | Knapsack Problem                       | 19  |  |  |  |  |  |

|    |                | 2.1.4       | Travelling Salesman Problem            | 22  |  |  |  |  |  |

|    |                | 2.1.5       | Manhattan Tourist Problem              | 24  |  |  |  |  |  |

|    |                | 2.1.6       | All Pairs. Shortest Path Problem       | 25  |  |  |  |  |  |

xii Table of contents

|   | 2.2 | Dynan    | nic Programming                              | 27         |

|---|-----|----------|----------------------------------------------|------------|

|   |     | 2.2.1    | Definition                                   | 27         |

|   |     | 2.2.2    | Dynamic Programming Methods                  | 30         |

|   |     | 2.2.3    | Solving Problems Through Dynamic Programming | 30         |

|   | 2.3 | Altern   | ative Solving Methods                        | 36         |

|   |     | 2.3.1    | Inexact Methods                              | 36         |

|   |     | 2.3.2    | Exact Methods                                | 38         |

|   | 2.4 | Paralle  | el Programming                               | 40         |

|   |     | 2.4.1    | Parallelism                                  | 41         |

|   |     | 2.4.2    | NVIDIA CUDA                                  | 44         |

|   |     | 2.4.3    | Existing Parallel Methods                    | 49         |

| • | 3.6 |          |                                              | <i>(</i> 2 |

| 3 |     | lel Desi |                                              | 63         |

|   | 3.1 | Design   | 1                                            | 64         |

|   |     | 3.1.1    | An Anti-Diagonal Approach                    | 64         |

|   |     | 3.1.2    | Memory Structure                             | 68         |

|   |     | 3.1.3    | File Format                                  | 73         |

|   | 3.2 | Impler   | mentation                                    | 75         |

|   |     | 3.2.1    | Thread Model                                 | 75         |

|   |     | 3.2.2    | Memory                                       | 78         |

|   |     | 3.2.3    | Thread Model II                              | 82         |

|   |     | 3.2.4    | Performance Validation                       | 85         |

|   |     | 3.2.5    | Input File Implementation                    | 89         |

|   |     | 3.2.6    | Other Implementation Details                 | 93         |

|   | 3.3 | Compa    | arison to Existing Work                      | 96         |

|   |     |          |                                              |            |

| 4 | App | lication | of the Model                                 | 101        |

| Table of contents | xiii |

|-------------------|------|

|   | 4.1  | Proble  | m Implementation                             | 102 |

|---|------|---------|----------------------------------------------|-----|

|   |      | 4.1.1   | Longest Common Subsequence Problem           | 102 |

|   |      | 4.1.2   | The Manhattan Tourist Problem                | 103 |

|   |      | 4.1.3   | The Knapsack Problem                         | 104 |

|   | 4.2  | Availa  | ble General Optimisations                    | 106 |

|   | 4.3  | Specia  | llised Problems                              | 107 |

|   |      | 4.3.1   | The Travelling Salesman Problem              | 107 |

|   |      | 4.3.2   | All Pairs, Shortest Path APSP Problem        | 109 |

|   |      | 4.3.3   | Defining Unsuitable and Inefficient Problems | 110 |

| 5 | Test | ing Met | thodology                                    | 113 |

|   | 5.1  | Testing | g Environment and Hardware                   | 114 |

|   | 5.2  | Metho   | dology                                       | 114 |

|   |      | 5.2.1   | CUDA Metrics                                 | 114 |

|   |      | 5.2.2   | Empirical Metrics                            | 117 |

|   |      | 5.2.3   | Global Testing Parameters                    | 119 |

|   |      | 5.2.4   | Test Data                                    | 119 |

|   | 5.3  | Compa   | arative Data                                 | 123 |

|   |      | 5.3.1   | Sequential CPU                               | 124 |

|   |      | 5.3.2   | Parallel CPU                                 | 125 |

|   |      | 5.3.3   | Parallel GPU                                 | 126 |

|   | 5.4  | Refere  | ence Benchmarks                              | 127 |

| 6 | Perf | ormano  | ce Testing                                   | 131 |

|   | 6.1  | Perfor  | mance on the Test Problems                   | 132 |

|   |      | 6.1.1   | The Longest Common Sub Sequence Problem      | 132 |

|   |      | 6.1.2   | Edit Distance Problem                        | 137 |

**xiv** Table of contents

|    |        | 6.1.3   | The Knapsack Problem            | 142 |

|----|--------|---------|---------------------------------|-----|

|    |        | 6.1.4   | The Manhattan Tourist Problem   | 147 |

|    |        | 6.1.5   | The Travelling Salesman Problem | 151 |

|    | 6.2    | Compa   | arative Benchmarks              | 155 |

|    |        | 6.2.1   | Sequential CPU                  | 155 |

|    |        | 6.2.2   | Parallel CPU                    | 162 |

|    |        | 6.2.3   | Parallel GPU                    | 168 |

|    | 6.3    | Key Fi  | indings                         | 172 |

| 7  | Con    | clusion |                                 | 175 |

|    | 7.1    | Introdu | uction                          | 176 |

|    | 7.2    | Overal  | ll Model Performance            | 177 |

|    | 7.3    | Memo    | ry Management                   | 178 |

|    | 7.4    | CUDA    | Efficiency                      | 179 |

|    | 7.5    | File Fo | ormat Effectiveness             | 180 |

|    | 7.6    | Future  | Work                            | 181 |

| Re | eferen | ces     |                                 | 183 |

# **List of figures**

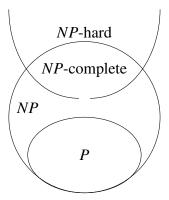

| 2.1 | How the different complexity classes interact and overlap in terms of $P$ and $NP$               | 13 |

|-----|--------------------------------------------------------------------------------------------------|----|

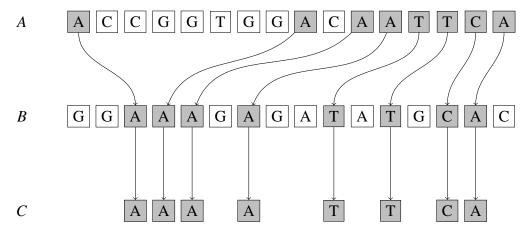

| 2.2 | The longest common subsequence $(C)$ being extracted from two input strings                      |    |

|     | (A  and  B)                                                                                      | 15 |

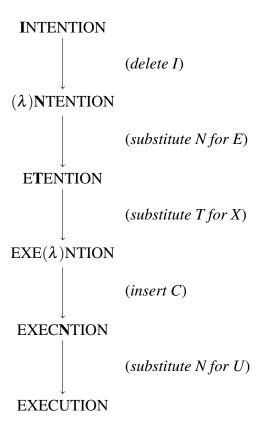

| 2.3 | The edit distance moving from the string INTENTION to EXECUTION,                                 |    |

|     | which has a Levenshtein distance of 8                                                            | 18 |

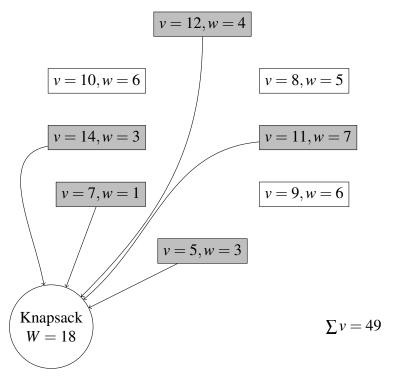

| 2.4 | A knapsack instance where the subset of optimal items from a given set of                        |    |

|     | input items is highlighted                                                                       | 21 |

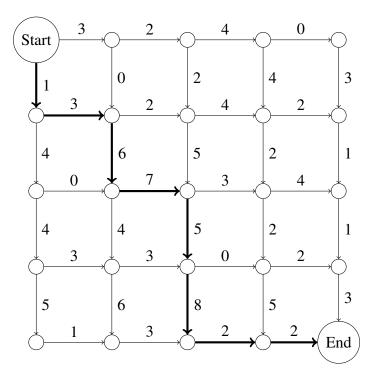

| 2.5 | A Manhattan tourist problem instance. The number of landmarks on each                            |    |

|     | street denoted as the weight of the edges, the optimal solution is highlighted                   |    |

|     | in the figure                                                                                    | 24 |

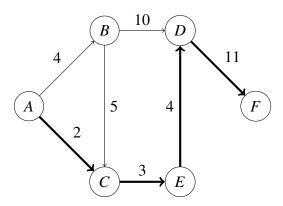

| 2.6 | A directed graph with the cost shown for traversing each edge, highlighting                      |    |

|     | the shortest path from $A$ to $F$                                                                | 26 |

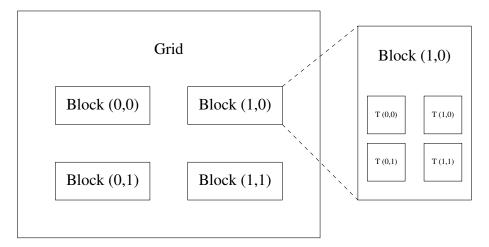

| 2.7 | A representation of the block and thread hierarchy adopted by the NVIDIA                         |    |

|     | CUDA. T denotes individual threads                                                               | 45 |

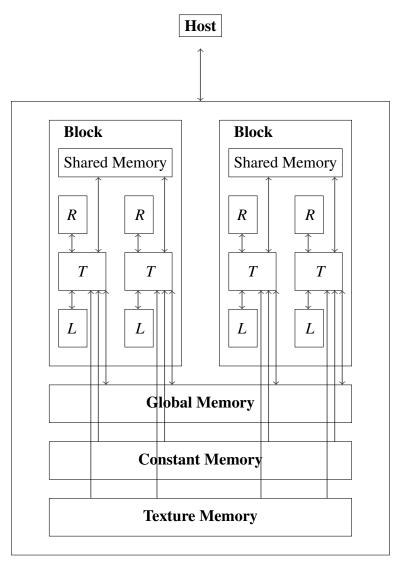

| 2.8 | The memory hierarchy of a graphics processing unit, and how these different                      |    |

|     | memory stores interact. $R = \text{registers}$ , $T = \text{thread}$ , $L = \text{local memory}$ | 47 |

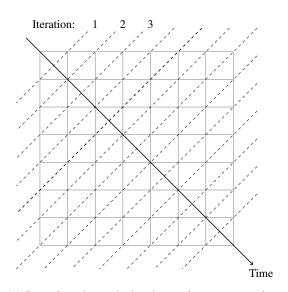

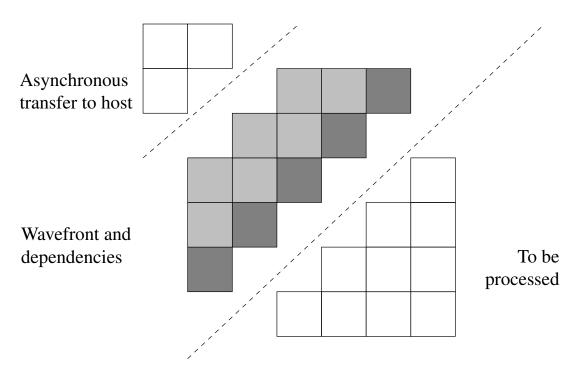

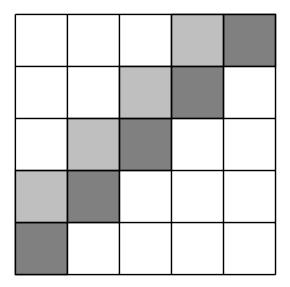

| 3.1 | How the method of traversing through the dynamic programming scoring                             |    |

|     | grid in a diagonal manner, to allow parallel solving, operates                                   | 65 |

xvi List of figures

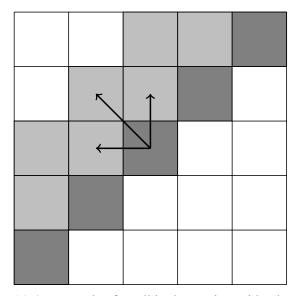

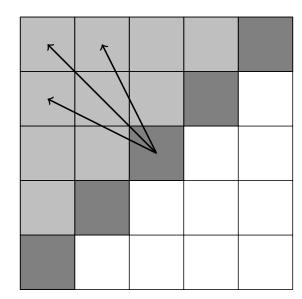

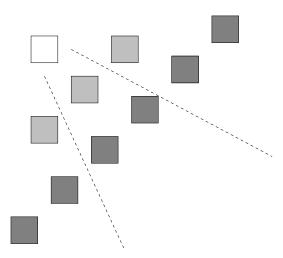

| 3.2  | Different problems require different previous diagonal iterations to be stored,    |    |

|------|------------------------------------------------------------------------------------|----|

|      | due to the dependencies. Dark grey cells denote the current iteration, lighter     |    |

|      | grey cells previous iterations, arrows the dependencies                            | 67 |

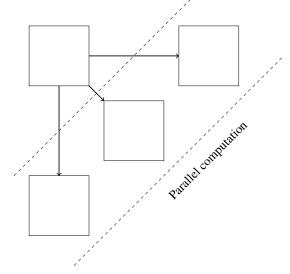

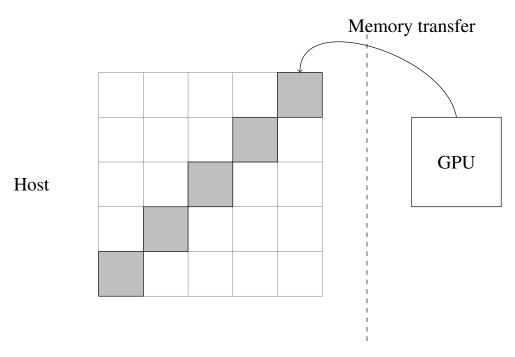

| 3.3  | Iterations can be transferred back from the GPU to the host when they are no       |    |

|      | longer required                                                                    | 70 |

| 3.4  | Iterations of the wave front are transferred from the GPU to the complete          |    |

|      | scoring grid which is maintained on the host                                       | 71 |

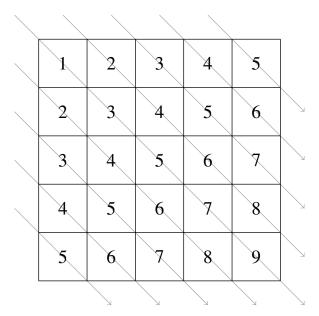

| 3.5  | A naive thread traversal method of the proposed model based on the design          |    |

|      | thus far, where the values in each cell represent which iteration they will be     |    |

|      | populated in                                                                       | 76 |

| 3.6  | The actual thread mapping we adopt. Numbers in each cell denote the                |    |

|      | iteration number of the wave front, and grey arrows show which threads are         |    |

|      | responsible for calculating which cell of the scoring grid                         | 77 |

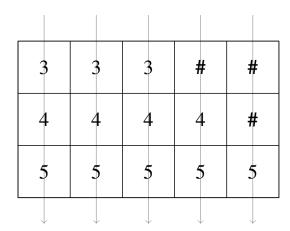

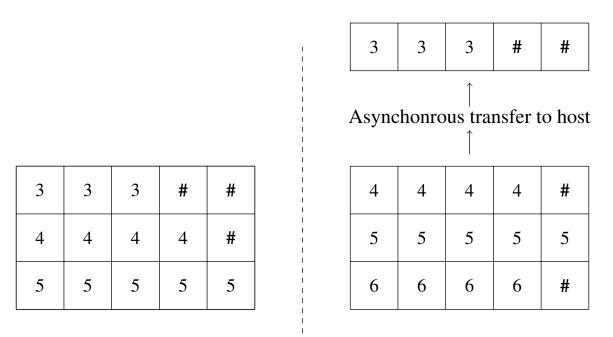

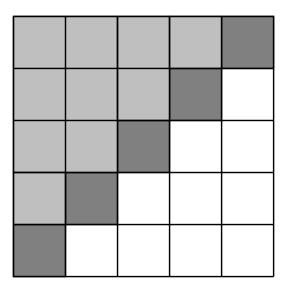

| 3.7  | The memory model which supports the parallel model. Numbers within the             |    |

|      | cell denote the iteration of wavefront the cell belongs to, '#' denotes the        |    |

|      | memory has been allocated, but is not currently being used by the model            | 79 |

| 3.8  | The memory model which supports the parallel model, showing that at all            |    |

|      | times, threads have work, and memory allocated to perform this work in.            |    |

|      | Numbers within the cell denote the iteration of wavefront the cell belongs to      | 80 |

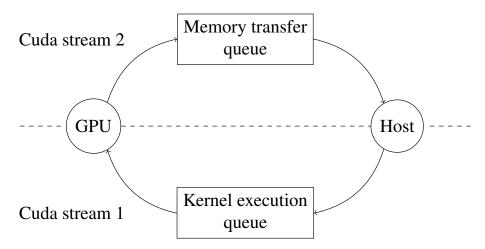

| 3.9  | Multiple CUDA streams are used to allow the asynchronous operations of             |    |

|      | data transfer and processing                                                       | 81 |

| 3.10 | Block division where the block size is four, and the size of the largest iteration |    |

|      | of the wave front is five                                                          | 84 |

| 3.11 | The memory used when the longest iteration is 10 wide, spread across two           |    |

|      | blocks                                                                             | 85 |

List of figures xvii

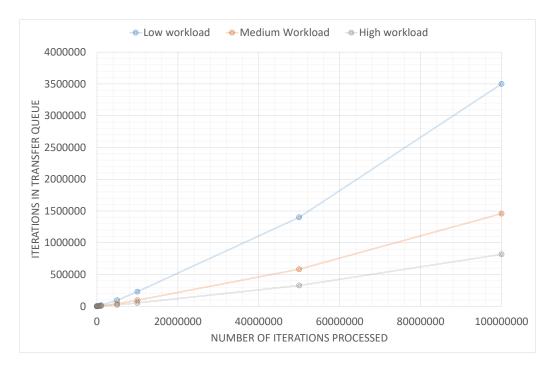

| 3.12 | Number of iterations still in the asynchronous transfer queue at the end of     |     |

|------|---------------------------------------------------------------------------------|-----|

|      | execution for differing workloads of wave front calculation                     | 87  |

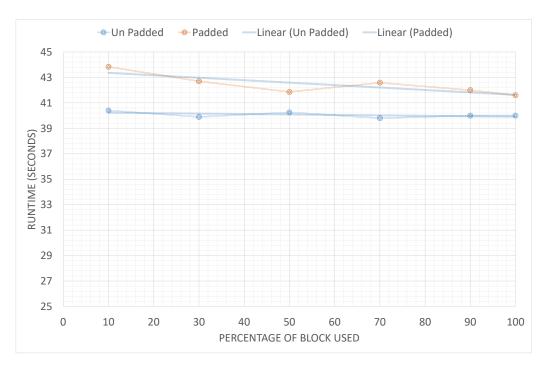

| 3.13 | The effect that padding unused data has on the runtime of algorithm, as the     |     |

|      | amount of unused data in a given block decreases                                | 88  |

| 3.14 | A complete input file for a longest common subsequence problem, with two        |     |

|      | input strings 5 characters in length, stored in constant memory on the GPU,     |     |

|      | maintaining the entire scoring grid                                             | 90  |

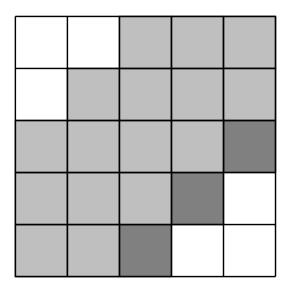

| 4.1  | Dependencies of the wavefront when solving the longest common subse-            |     |

|      | quence problem                                                                  | 102 |

| 4.2  | Dependencies of the wavefront when solving the Manhattan tourist problem        | 103 |

| 4.3  | Dependencies of the wavefront when solving the knapsack problem                 | 104 |

| 4.4  | Dependencies of the wavefront when solving the knapsack problem, once           |     |

|      | the wavefront is more than halfway through the scoring grid                     | 105 |

| 4.5  | Multiple subgrids are required to solve the travelling salesman problem         | 108 |

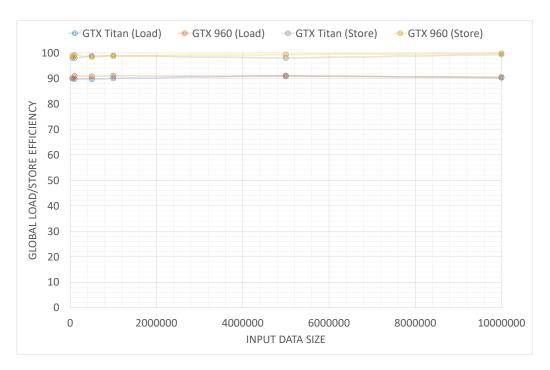

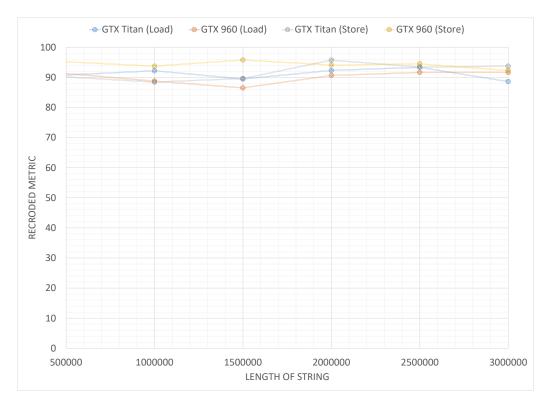

| 5.1  | Efficiency of the global load and store operations whilst running the reference |     |

|      | implementation, as the size of the scoring grid increases                       | 128 |

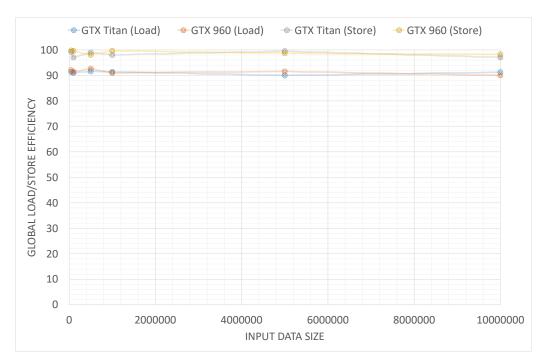

| 5.2  | Recorded CUDA metrics whilst running the reference implementation, as           |     |

|      | the size of the scoring grid increases                                          | 129 |

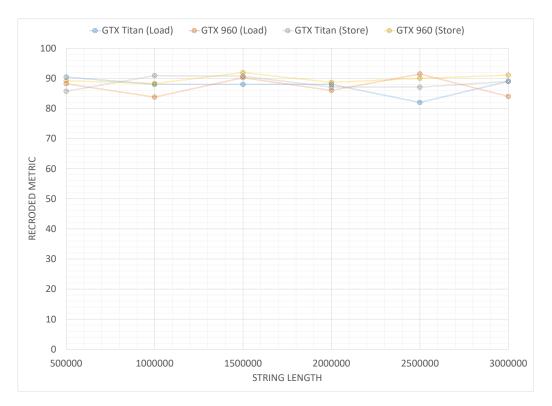

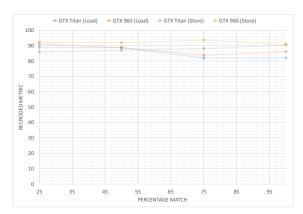

| 6.1  | Recorded global load and store efficiency whilst solving the longest common     |     |

|      | subsequence problem, on two strings of equal, increasing length, when the       |     |

|      | match is 50% of each string                                                     | 132 |

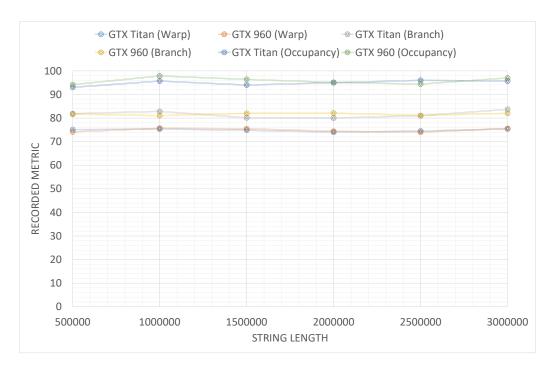

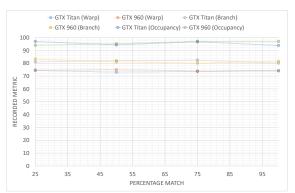

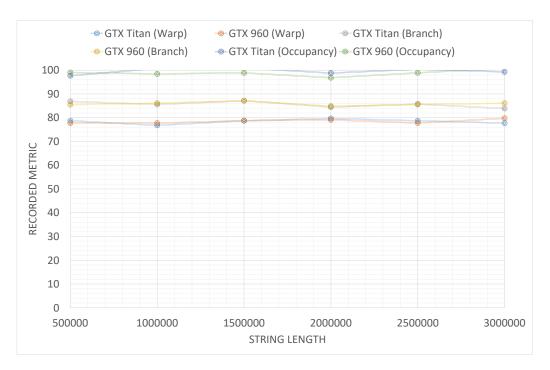

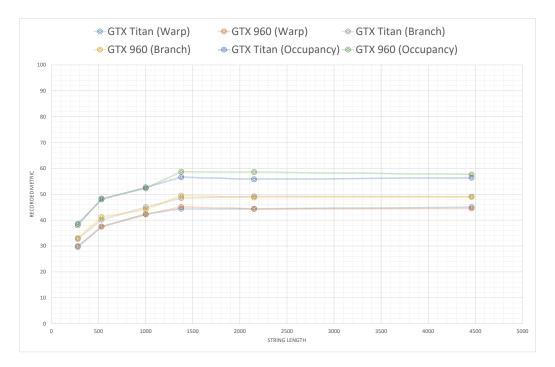

| 6.2  | Recorded CUDA metrics whilst solving the longest common subsequence             |     |

|      | problem, on two strings of equal, increasing length, when the match is 50%      |     |

|      | of each string                                                                  | 133 |

xviii List of figures

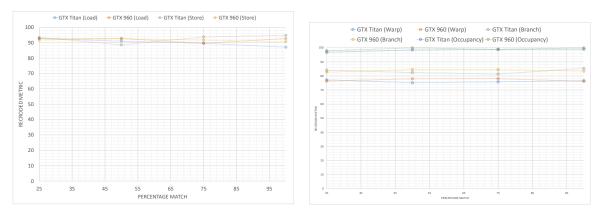

| 6.3  | Metrics recorded when solving the longest common subsequence problem          |     |

|------|-------------------------------------------------------------------------------|-----|

|      | with a fixed string length of 3,000,000 and the longest common subsequence    |     |

|      | between the strings is varied between 25% and 100%                            | 134 |

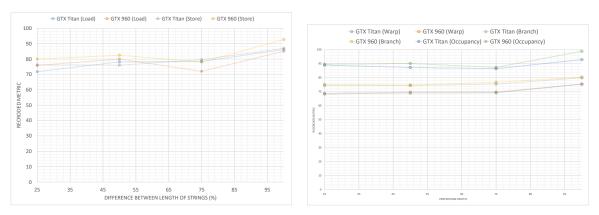

| 6.4  | Metrics recorded when solving the longest common subsequence problem          |     |

|      | with a fixed string length of 3,000,000 for the first string, and the second  |     |

|      | string length is altered between 25% and 100% of this                         | 135 |

| 6.5  | Recorded global load and store efficiency whilst solving the edit distance    |     |

|      | problem, on two strings of equal, increasing length, when the match is $50\%$ |     |

|      | of each string                                                                | 137 |

| 6.6  | Recorded CUDA metrics whilst solving the edit distance problem, on two        |     |

|      | strings of equal, increasing length, when the match is $50\%$ of each string  | 138 |

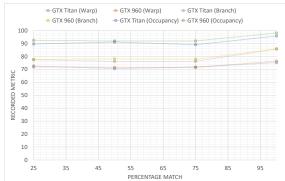

| 6.7  | Metrics recorded when solving the edit distance problem with a fixed string   |     |

|      | length of 3,000,000, and the amount of commonality between the strings is     |     |

|      | varied between 25% and 100%                                                   | 139 |

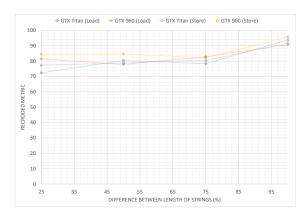

| 6.8  | Metrics recorded when sovling the edit distance problem with a fixed string   |     |

|      | length of 3,000,000 for the first string, and a second string length altered  |     |

|      | between 25% and 100% of this                                                  | 140 |

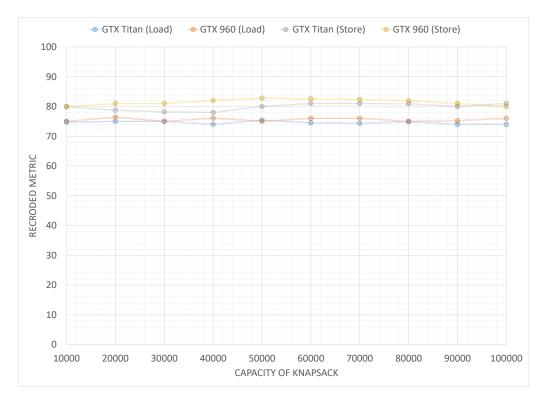

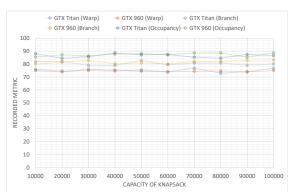

| 6.9  | Recorded global load and store efficiency whilst solving the 0/1 knapsack     |     |

|      | problem, as the capacity of the knapsack and associated item set increases .  | 142 |

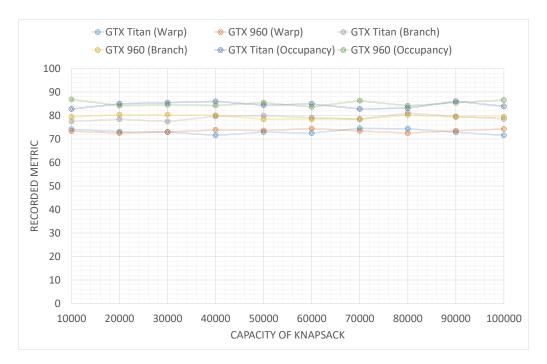

| 6.10 | Other recorded CUDA metrics whilst solving the 0/1 knapsack problem, as       |     |

|      | the capacity of the knapsack and associated item set increases                | 143 |

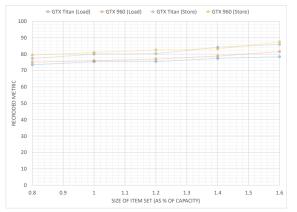

| 6.11 | Metrics recorded when sovling the 0/1 knapsack problem with a fixed capac-    |     |

|      | ity of 50,000, and the size of the item set is altered between runs           | 145 |

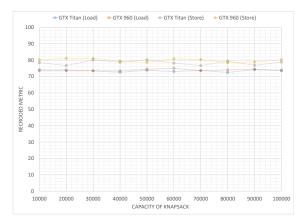

| 6.12 | Metrics recorded when running the bounded knapsack problem with varying       |     |

|      | capacities, and a fixed item set size of 1% of the capacity                   | 146 |

List of figures xix

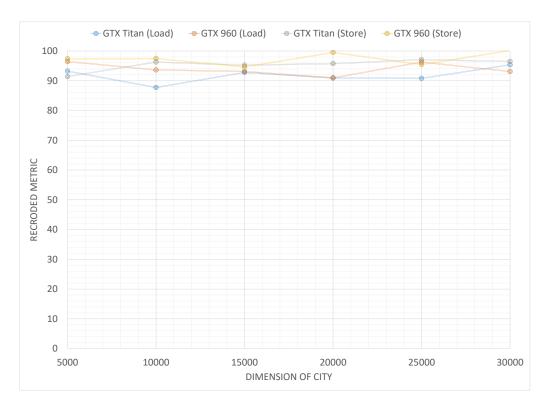

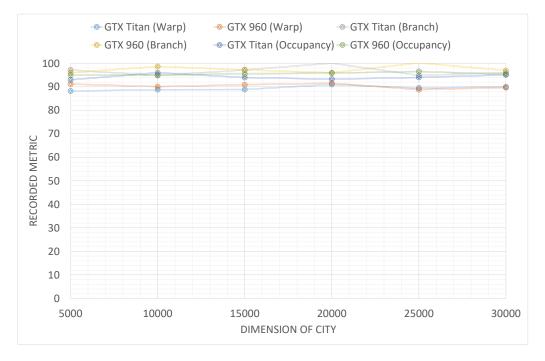

| 6.13 | Recorded global load and store efficiency whilst solving the Manhattan         |     |

|------|--------------------------------------------------------------------------------|-----|

|      | tourist problem, as the dimension of the city grid increases                   | 148 |

| 6.14 | Other recorded CUDA metrics whilst sovling the Manhattan tourist problem,      |     |

|      | as the dimension of the city grid increases                                    | 148 |

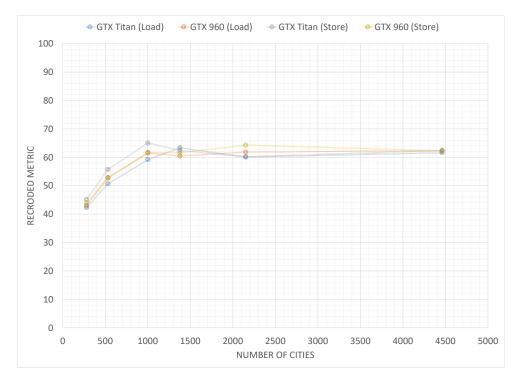

| 6.15 | Recorded global load and store efficiency whilst solving the travelling sales- |     |

|      | man problem, as the number of cities increases                                 | 151 |

| 6.16 | Other recorded CUDA metrics whilst solving the travelling salesman prob-       |     |

|      | lem, as the number of cities increases                                         | 153 |

| 6.17 | Runtime for sequential CPU algorithms, compared to our proposed model          |     |

|      | when solving the longest common subsequence problem, as the size of the        |     |

|      | string grows                                                                   | 157 |

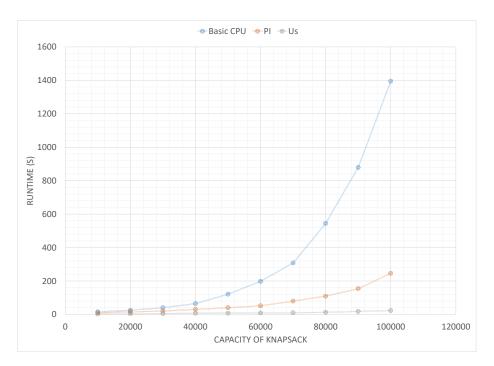

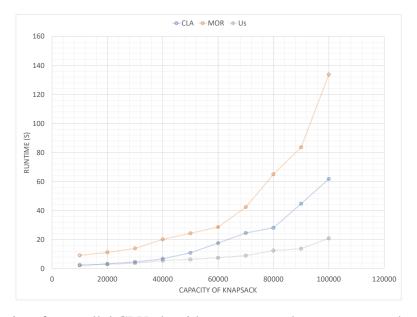

| 6.18 | Runtime of sequential CPU algorithms, compared to our parallel model when      |     |

|      | solving the $0/1$ knapsack problem, as the capacity of the knapsack grows      | 160 |

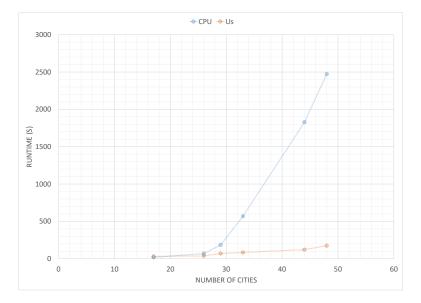

| 6.19 | Runtime for a sequential CPU algorithm, compared to our parallel model         |     |

|      | when solving the travelling salesman problem as the number of cities grows     | 161 |

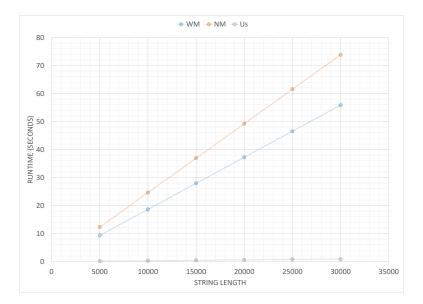

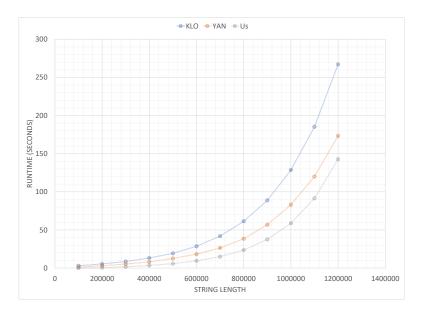

| 6.20 | Runtime for parallel CPU algorithms, compared to our parallel model when       |     |

|      | solving the longest common subequence problem as the string length grows       | 163 |

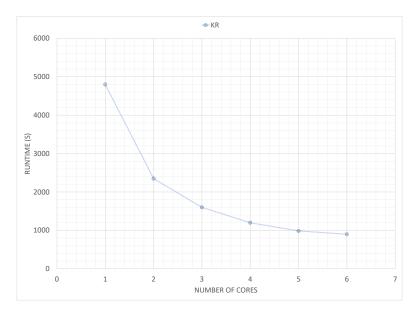

| 6.21 | Runtime for the parallel CPU based KR algorithm solving the longest com-       |     |

|      | mon subsequence problem as the number of cores is increased                    | 165 |

| 6.22 | Runtime for parallel CPU algorithms, compared to our proposed parallel         |     |

|      | model when solving the 0/1 knapsack problem, as the capacity of the knap-      |     |

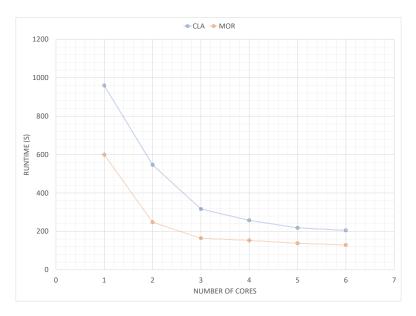

|      | sack grows                                                                     | 166 |

| 6.23 | Runtime for the parallel CPU based CLA and MOR algorithm solving the           |     |

|      | knapsack problem as the number of cores is increased                           | 167 |

xx List of figures

| 6.24 | recorded run-times for our our model when solving the longest common    |     |  |  |

|------|-------------------------------------------------------------------------|-----|--|--|

|      | subsequence problem as the string length varies, compared to other GPU  |     |  |  |

|      | based algorithms                                                        | 170 |  |  |

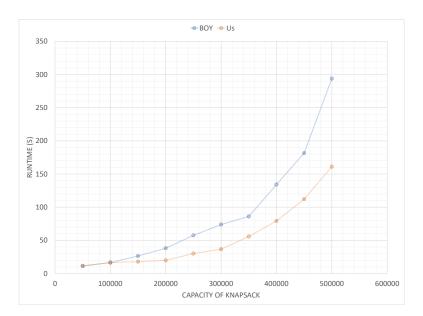

| 6.25 | Runtimes for our our model when solving the 0/1 knapsack problem as the |     |  |  |

|      | capacity varies, compared to another GPU based algorithm                | 172 |  |  |

# List of tables

| 3.1 | Results of the CUDA branch efficiency metric when running on both padded    |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | and unpaded data, as the percentage of 'used' data increases                | 89  |

| 6.1 | Average instructions per clock recorded during the performance testing of   |     |

|     | the longest common subsequence problem                                      | 136 |

| 6.2 | Average instructions per clock recorded during the performance testing of   |     |

|     | the edit distance problem                                                   | 141 |

| 6.3 | Average instructions per clock values recorded during the performance test- |     |

|     | ing of the 0/1 knapsack problem                                             | 147 |

| 6.4 | Average instructions per clock values recorded during the performance test- |     |

|     | ing of the Manhattan tourist problem                                        | 150 |

| 6.5 | Average instructions per clock recorded during the performance testing of   |     |

|     | the travelling salesman problem                                             | 154 |

| 6.6 | Comparative runtimes for sequential CPU based LCS algorithm, and our        |     |

|     | parallel model                                                              | 156 |

| 6.7 | Comparative runtimes for a sequential CPU based edit distance algorithms,   |     |

|     | and our parallel model                                                      | 157 |

| 6.8 | Comparative runtimes for a sequential CPU based manhattan distance prob-    |     |

|     | lem, and our parallel model                                                 | 158 |

**xxii** List of tables

| 6.9  | Comparative runtimes for a sequential CPU based 0/1 knapsack problem      |     |  |

|------|---------------------------------------------------------------------------|-----|--|

|      | algorithm, and our parallel model                                         | 159 |  |

| 6.10 | Comparative runtimes for a sequential CPU based travelling salesman prob- |     |  |

|      | lem solver, and our parallel model                                        | 161 |  |

| 6.11 | Comparative runtimes for a parallel CPU based longest common subsequence  |     |  |

|      | problem solver, and our parallel model                                    | 163 |  |

| 6.12 | Runtimes for our model compared to two parallel CPU based knapsack        |     |  |

|      | problem solvers                                                           | 166 |  |

| 6.13 | Runtimes for our model compared to two parallel GPU based longest com-    |     |  |

|      | mon subsequence solvers                                                   | 169 |  |

| 6.14 | Comparative runtimes for parallel GPU based 0/1 knapsack algorithm com-   |     |  |

|      | pared to our model                                                        | 171 |  |

## Chapter 1

### Introduction

#### **Overview**

This thesis presents a generic parallel model that seeks to enable a subset of optimisation problems to be solved, both quickly and efficiently, through the use of Graphic Processing Unit (GPU) based techniques. A parallel model is a method of mapping algorithms and data to multiple processors by splitting it into multiple parts, such that all parts can be executed simultaneously in an effort to reduce computation time. A GPU is a highly parallel processing unit, originally designed to render 3D images, but more recently can be utilised for general purpose programming. Performance metrics have been taken using specialised GPU profiling tools to validate the efficiency of the proposed model. Also described is a file format which seeks to allow the implementation of optimisation problems on the GPU, with minimal programming knowledge from the end user. Analysis and discussion of the observed metrics allows conclusions to be drawn on the suitability and applicability of the model in different scenarios.

In this chapter a high level overview of the work detailed in the thesis is presented, as well as the contributions stemming from this. Also in this chapter is an outline of the thesis structure.

2 Introduction

#### 1.1 Introduction

Solving discrete optimisation problems exactly is desirable, as, by definition, this is guaranteed to provide the optimal solution. This thesis is focused on the field of solving optimisation problems through the use of general purpose graphics processing unit (GPGPU) programming. "Driven by the insatiable market demand for real-time, high-definition 3D graphics, the programmable Graphic Processor Unit or GPU has evolved into a highly parallel, multithreaded, many-core processor with tremendous computational horsepower and very high memory bandwidth" [71]. GPGPU programming is a relatively new field of programming, which allows end users to program GPUs for uses other than the purpose of rendering 2D images of 3D spaces: "graphics processors (GPUs) become attractive because they offer extensive resources even for non-visual, general-purpose computations: massive parallelism, high memory bandwidth, and general purpose instruction sets, including support for both single-precision and double-precision [...] arithmetic" [17]. GPUs in many applications can prove to be considerably faster than their CPU counterparts; "the reason behind the discrepancy in floating-point capability between the CPU and the GPU is that the GPU is specialised for compute-intensive, highly parallel computation [...] and is therefore designed such that more transistors are devoted to data processing rather than data caching and flow control" [84]. This has led to the rise of languages to support the implementation of programs on the GPU such as the proprietary, closed source, NVIDIA CUDA [70] - NVIDIA Compute Unified Device Architecture, which allows programs to be deployed on NVIDIA hardware, and the focus of this thesis is limited to CUDA. However, the unique architecture of the GPU presents unique programming challenges [31, 98], and developing parallel models to efficiently use the GPU is important: "... should redirect efforts in GPGPU research from ad-hoc porting of applications to establishing principles and strategies that allow efficient mapping of computation to graphics hardware" [82].

1.1 Introduction

More specifically, this thesis considers using the extensive computational resources of the GPU to accelerate the solving of classic, hard problems with high computational complexities, through the use of a technique called dynamic programming [19]. These common problems form the core of many real world algorithms, from vehicle routing to cryptography, and any performance gains should be widely beneficial. The solving methods considered here are exclusively exact methods, meaning this work not only improves run time but also guarantees solution quality is not only maintained, but is in fact maximised, and possibly improved over inexact methods. This is done with the motivation that GPUs have such a high number of cores, exact solving may be possible for hard problems.

As aforementioned [82], much of the previous work relating to the development of dynamic programming algorithms for deployment on the GPU has been targeted specifically at individual problems, rather than looking at overarching parallel methods. Considering only some of the test problems described within this thesis, a range of algorithms specifically targeting each is available [14, 99, 41]. We present instead a single, generic model that is suitable for a range of problems, even beyond the ones for which it was originally designed. As such, the study of a model for a wide range of uses such as this, is a novel direction of research. The work presented in this thesis contributes further knowledge to the discussion on developing suitable parallel models that target GPGPU hardware for a wide range of problems.

To allow the implementation of a range of different problems we present a basic syntax which defines the problem function, input data and type, and some implementation parameters, allowing an end user to implement further problems easily. All test problems in this thesis, which are defined as suitable for parallelism through the model, are implemented through this syntax, demonstrating its validity.

Changing how the data maps to the physical hardware of GPU, through parameters such as the block size, can have an effect on both run-time and resource utilisation. This thesis

4 Introduction

also examines the effect the choice of mapping strategy has, and what factors influence this, such as: the specific problem; the class of problem; or whether selecting the optimal strategy is problem agnostic and merely a factor of our model. Correctly mapping data to the hardware is found to have a significant impact on the performance of the parallelism, with slight differences from problem to problem, and this is discussed in detail in the performance results.

The thesis provides an analysis of the model in terms of efficiency, using NVIDA CUDA based metrics, meaning not only the run time is considered – it should be assumed a device with hundreds of cores will improve the run-time – but also how effectively the available underlying resources of the GPU are being used. This analysis gives insight to the performance of the model, not restricted to the test problems examined in this thesis, allowing predictions to be made as to how it will perform more generally for different problems and on future iterations of GPU hardware.

#### 1.2 Thesis Aims

The main aim of this thesis is to present an abstract and generic solving methodology that enables the mapping of optimisation problems, which can be solved through dynamic programming techniques, onto the graphics processing unit with the goal of improving the run-time of these computationally challenging problems. It aims to provide an investigation into how to effectively solve these problems using the GPU, considering other factors beyond run-time such as memory efficiency and other overheads inherent in GPU programming. Through this, we aim to increase the knowledge related to running this class of problem on a GPU.

1.3 Contributions 5

#### 1.3 Contributions

The main contributions offered by this thesis are:

- A generic parallel model which runs on the GPU that, through the use of dynamic programming techniques, allows a subset of optimisation problems to be solved by effectively using the high performance computing facilities offered by the GPU architecture. Problems which can be solved include the the longest common subsequence problem, the travelling salesman problem, and the knapsack problem. The exact range of problems that can be solved is dictated by the dependency structure of the specific problem this is discussed in detail in Section 3. The model is analysed and profiled, and performance figures are provided to demonstrate the effectiveness of the model.

- An efficient memory structure and memory management, that seeks to reduce the memory complexity on the GPU of the given input problems, allowing larger scale problem instances to be solved. This is an especially important consideration when running code on the GPU, as the amount of available memory is often more restrictive than normal programming environments, meaning it quickly limits the feasible problem size. As well as being memory efficient, it is required the model achieves this whilst simultaneously not causing excessive additional computational overhead. Again, profiling is used to validate that it achieves both goals.

- A generic file format based on Backus-Naur Form (BNF), that allows different problem definitions into be quickly input to the program. The file contains basic information about the problem to be solved, such as input data types, as well as information about the amount of memory the problem requires. This is then coupled with a very small function definition which defines the logic of the problem, and the mapping of the dynamic programming definition onto the input data, meaning that the model remains generic allowing new problems to be added quickly and easily.

6 Introduction

#### 1.4 Thesis Structure

This thesis is laid out as follows:

- Beginning in Chapter 2, the background work that underpins this thesis is presented, and relevant problems and literature are introduced. In Section 2.1 the test problems that have been selected are formally defined. In addition to a mathematical definition, both the computational and memory complexity required to solve them using naive approaches are given. Section 2.2 formally introduces and defines what is meant by the term *dynamic programming*, and provides the criteria that a problem must satisfy for dynamic programming to be applicable. Next we show how dynamic programming can be applied to solve the introduced test problems, and present some basic solving algorithms. Moving into Section 2.3, some alternate solving methodologies compared to dynamic programming are very briefly introduced, to help illustrate in which settings dynamic programming is appropriate. Finally, in Section 2.4, the concept of parallel programming is introduced and defined, as well as the benefits and drawbacks associated with it. The different paradigms of parallel programming are formally defined, and the GPU programming language we use, NVIDIA CUDA, is introduced and explained.

- Chapter 3 presents the model this thesis is proposing. Starting in Section 3.1, a high level design of the model is presented, demonstrating how it maps data to the physical resources of the GPU, and how the memory is managed when the model is in use. Next, in Section 3.2, the specifics of the implementation are considered, and small scale benchmarks are provided to justify the design decisions taken. This section also discusses in detail the file format used to allow new problems to be defined. The chapter concludes with Section 3.3, where we compare our model to the existing

1.4 Thesis Structure 7

algorithms available in the literature, and identify the main contributions our model offers.

- Next, Chapter 4 details how to implement the introduced problems using our parallel model. Section 4.2 goes on to introduce potential optimisations that can be made, without changing the overarching paradigm. In Section 4.3 we discuss which problems were found to be unsuitable for implementation through the model, or required it to be changed considerably, and attempt to classify the subset of problems that is suitable.

- Chapter 5 introduces the hardware that will be used for the analysis of the model, as well as the profiling and performance metrics that will be recorded during testing. Additionally, detail is given on how the test instances of each problem are generated. Also in this chapter, some reference benchmarks for the hardware used is provided to give an indication as to baseline and ideal performance.

- Moving into Chapter 6, we present the main performance results from the analysis

of the model, presenting results detailing run-time, and the recorded CUDA metrics.

We seek to generalise these results, in terms of the number of GPU blocks, and GPU

block sizes, allowing the results to be extrapolated and predictions made as to the

performance when running on alternate GPU hardware.

- Finally, Chapter 7 summarises the work, and draws conclusions based on the results that have been outlined in this thesis. In Section 7.6, some ideas and theories are presented as to the direction in which this work could be taken next.

8 Introduction

#### 1.5 Publications

#### 1.5.1 Model Design

The work presented in Chapter 3 covers the design of the generic parallel model, as well as how specific problems can be mapped onto the GPU using it.

An earlier version of this has been published in [74]:

O'Connell, J. F. & Mumford, C. L. (2014), An Exact Dynamic Programming Based Method to Solve Optimisation Problems Using GPUs, 347-353. In Proceedings of the Second International Symposium on Computing and Networking, IEEE.

#### doi:10.1109/CANDAR.2014.27

The performance of our parallel model is considered in terms of speed and computational efficiency when applied to instances of the knapsack problem, the longest common subsequence problem, and the travelling salesman problem.

In this paper we found our model performed well with all test problems, achieving a considerable level of speed up factor compared to the classic CPU implementation, as well as utilising the available resources of the GPU effectively. However, the paper posed further questions about improving the divergence of the code in order to improve the overall efficiency.

#### 1.5.2 Implementation

In Section 4.3.2 the implementation of the all pairs, shortest path problem on the GPU is described. The algorithm detailed here has been used to support the work in the following submitted journal article:

1.5 Publications 9

• John, M. P., Mumford, C. L, Lewis, R, O'Connell, J. F. Exploring design issues for solving the urban transit routing problem using a multi-objective evolutionary algorithm. In IEEE Transactions on Evolutionary Computation. *Under review*.

A parallel implementation of the all pairs shortest path problem is used to support the implementation of an algorithm which uses meta-heuristic techniques, in an effort to design efficient bus route networks based on an underlying road network.

Whilst the focus of the article was not that of the performance of the GPU implementation, it does discuss the fact that the GPU implementation of the all pairs shortest path problem produces run times several hundred times better than that of the classic serial CPU counterpart. The study also notes that as the problem size increases, the speedup factor offered by the GPU also increases, until it becomes steady near the 800% mark.

#### **Summary**

In this chapter the thesis topic was introduced, as well as the motivation for undertaking the work detailed within. The key contributions offered were detailed, and an overall structure of the following document was presented. The next chapter will introduce the background concepts upon which the work in this thesis builds.

# Chapter 2

## **Background**

#### **Overview**

This chapter introduces background topics and problems, as well as existing work using NVIDIA CUDA 6.5 [52], that is relevant to the research in this thesis.

Beginning in Section 2.1, the problems which this thesis is concerned with solving are introduced and defined: namely, the longest common subsequence problem and the edit distance problem, the knapsack problem, the all pairs shortest path problem and the Manhattan tourist problem. Both graphical representations and mathematical definitions of these are provided.

Moving into Section 2.2, the method of programming and solving a problem, called *dynamic programming* [9], is introduced. The benefits and drawbacks of using such an approach to solve a problem are considered. The solution methodologies based on dynamic programming techniques for the introduced problems are defined.

Next, in Section 2.3, other alternative classical methods of solving the aforementioned problems are considered and discussed. We address *inexact* solving methodologies, heuristic and meta-heuristic methods, as well as *exact* methods.

12 Background

Finally, in Section 2.4, parallel programming is introduced. Discussed are the concepts of parallel programming, the different paradigms, as well as the common use cases and issues associated with it. Next we consider how effectively a dynamic programming based algorithm can be mapped onto a parallel processing model. Lastly, the programming model offered by NVIDIA CUDA is outlined, before finally discussing existing algorithms and models that employ the CUDA programming environment in order to solve the introduced problems.

Fig. 2.1 How the different complexity classes interact and overlap in terms of P and NP

#### 2.1 Problem Introduction

Introduced in this section are the problems we are seeking to solve with the parallel model presented by this thesis. Whilst all of these are easily solved for limited size instances, due to the high computational complexity they very quickly become in-feasible to solve exactly as the size of the problem grows. It is therefore very common to solve these inexactly using methods such as heuristics. However, as parallel programming seeks to reduce the run time of executing a program, these problems stand to benefit from being implemented in parallel as this will allow larger instances to be solved exactly.

#### 2.1.1 NP Complexity

All problems which will be introduced fall under the complexity class of *NP*, therefore we first define this. The 'P' in *NP* is defined as the computational complexity when a decision problem can be solved by a deterministic Turing machine, requiring a polynomial amount of computation proportional to the size of the input. Corbham's thesis states that, generally, a problem can be solved feasibly on a computation device if the problem lies within the *P* class [40]. Obviously this is still highly dependent on the size of the input, but is a good starting point when considering the feasibility of solving a problem.

14 Background

The computation class NP refers to non-deterministic polynomial time problems. These are the class of decision problems where correct solutions to the problem can be accepted by a non-deterministic Turing machine in polynomial time. The complexity class P is contained within the larger class of NP.

*NP*-complete problems are problems which are enclosed in both the NP and NP-hard complexity classes. Although solutions to these problem can be verified in polynomial time, there is no quick way of generating the solution in the first place. Formally, this is defined as: a problem *p* in the class *NP* is *NP*-complete, if all other problems in *NP* can be transformed to *p* in polynomial time. An example of reducing an *NP*-complete problem to different *NP*-complete problems is reducing the travelling salesman problem to the Hamiltonian cycle problem, which in turn can be reduced again to the vertex cover problem. Generally, *NP*-complete problems are considered more difficult to solve than *NP*, because if there is a method of quickly solving an *NP*-complete problem, there is a quick method of solving all *NP* problems (as every problem in *NP* can be reduced to an *NP*-complete problems). As there is no computationally quick way of generating solutions to these problems, they are commonly solved through the use of approximation algorithms, or heuristic methods. These methods generate solutions to the problem, albeit ones that may not be optimal. The relationship between the classes is shown in Fig. 2.1.

When discussing *NP*-complete problems, it is a common misconception that the *NP* stands for *non polynomial* time, referring to the fact there is no know polynomial time algorithm to solve the problem. Whilst this is likely true, as these problems are so difficult to solve, this has never been proven.

NP-hard problems are problems which are at least as hard as the hardest problem within the NP class. However, they are not required to be decision problems, nor in the NP class at all. Formally, a problem p is NP-hard if there is an NP-complete problem p which can be reduced in polynomial time to p. As all NP-complete problems can be reduced to any

Fig. 2.2 The longest common subsequence (C) being extracted from two input strings (A and B)

other *NP*-complete problem in polynomial time, all *NP*-complete problems can be reduced to *NP*-hard problems. An example of an *NP*-hard problem is the halting problem - given a program, and an input, will it halt? This is a decision problem but it is not in *NP*, yet it is clear that any *NP*-complete problem can be reduced to this.

## 2.1.2 The Longest Common Subsequence Problem

"String comparison is a central operation in various environments: a spelling error correction program tries to find the dictionary entry which resembles most a given word, in molecular biology we want to compare two DNA or protein sequences to learn how homologous they are, in a file archive we want to store several versions of a source program compactly by storing only the original version" [11]

The longest common subsequence (LCS) problem has the goal of finding the longest subsequence that is common to a given set of input sequences. This input set is commonly assumed to consist of two sequences, but there is no limit and *n* sequences can be analysed, although each additional sequence increases the computational complexity.

The problem is well defined by Hirschberg [43]. String  $C = c_1, c_2, \ldots, c_i, \ldots, c_p$  is a subsequence of string  $A = a_1, a_2, \ldots, a_i, \ldots, a_m$  if there is a mapping  $F : \{1, 2, \ldots, p\} \rightarrow \{1, 2, \ldots, k\}$  such that F(i) = k iff  $c_i = a_k$  and F is a strictly increasing function, where n is the length of the first string A, m is the length of the second string B, and p is the length of the subsequence C. C can be formed by deleting m - p (not necessarily adjacent) symbols from A.

From this a common subsequence is defined as: C is a common subsequence of A and  $B = b_1, b_2, \ldots, b_i, \ldots, b_n$  iff C is a subsequence of A and a subsequence of B. Therefore C is the longest common subsequence of A and B iff:

- C is a common subsequence of A and B

- There is no common subsequence D, for which the length of D is larger than C

A graphical example of the longest common subsequence problem can be found in Fig. 2.2.

For the general case of an arbitrary number of sequences, the problem is known to be NP-hard. To solve this through a simple naïve approach [60], assuming an input of N sequences, where the length of each sequence is defined as  $s_1, s_2, \ldots, s_i, \ldots, s_N$ , it would be a case of testing each of the  $2^{s_1}$  subsequences of the first input sequence to identify if they are subsequences of the remaining input sequences. These subsequences are checked in linear time for the remaining input sequences, which leads to the complexity of  $O\left(2^{s_1}\sum_{i>1}s_i\right)$ . Obviously this complexity is far too high to be practical for any reasonably sized input data.

The problem is of interest as it has many uses and provides the underpinning for a wide variety of different algorithms. The most common of these uses is that it is very prevalent in bio-informatics algorithms, as the structure of searching for subsequences is very similar to matching patterns within DNA and protein data [3, 76]. Here a parallel implementation could speed things up considerably, allowing longer strings to be analysed, or more strings to be analysed simultaneously.

This problem is also at the core of other algorithms such as compression algorithms or version control systems, as through the identification of subsequences it allows the difference between files, and lines of files, to be quickly identified [4]. Here a parallel version would simply reduce the execution time of such tools and utilities.

Due to the problems widespread uses, it has been the focus of much study, and as such there are many polynomial time algorithms available for when the size of the set of input strings is restricted, or when the alphabet available to the input strings is constrained. The most simplistic and widespread of these is a simple dynamic programming approach [43], which allows the solving of two string problems in polynomial time based on the length of the longest input string. These are discussed in detail in Sec. 2.2. Using this method compared to the brute-force approach reduces the computational complexity to O(mn), when only two input sequences are being processed, or  $O\left(N\prod_{i=1}^{N}s_i\right)$  for the general case where N is the number of input sequences, and s the length of each sequence.

### **Edit Distance**

The edit distance problem is a small extension to the longest common subsequence problem that seeks to apply metrics to the difference between two strings, and to apply a *cost*, or *distance*, that it would take to transform one string into another.

There are several methods to define the metrics used in the edit distance problem, and we chose to adopt a set of rules for our sample problems, called the Levenshtein distance [50]. The rules it defines for transforming a string are (where  $\lambda$  is the empty string):

- *Insertion* of a symbol. Inserting character c into string ab produces acb, or  $\lambda \to c$ .

- *Deletion* of a symbol. Deleting c from acb produces ab, or  $c \to \lambda$ .

- Substitution of a symbol. Substituting c for d in acb produces adb, or  $c \to d$ .

Fig. 2.3 The edit distance moving from the string *INTENTION* to *EXECUTION*, which has a Levenshtein distance of 8

Any arbitrary values can be applied to these scores; however, throughout this thesis we will assume that deletions and insertions have a cost of 1, and substitutions a cost of 2. Considering the example problem in Fig. 2.3, the presented string transformation would have an edit distance of 8.

As with the longest common subsequence, the algorithm has implications in bio-informatics processing, where the *optimal alignment* of two strings can be defined as the alignment of the two strings with the smallest edit distance [43].

The algorithmic implementation of this is very similar to the dynamic programming approach adopted to solve the longest common subsequence problem [94]. However, we also consider it as a test problem in this thesis as it demonstrates the usefulness of our model in solving different problems, when the underlying algorithms are altered to serve different purposes.

The benefits of parallelising the algorithm to solve this problem are very similar to that of parallelising the longest common subsequence problem: longer strings can be computed in a given time frame without the requirement of being separated into multiple smaller strings, as well as accelerating the computation of already feasible strings.

# 2.1.3 Knapsack Problem

"A well-known combinatorial problem that finds applications to capital budgeting problems, loading problems, and solutions of large optimization problems is the knapsack problem." [45]

The Knapsack Problem (KSP) is a combinatorial optimisation problem concerned with: given a set of items with an associated mass and profit value for each, select the subset of items such that a given capacity constraint is not violated by the cumulative mass of the items, whilst simultaneously maximising the cumulative profit of all the items selected.

There are many variants of the knapsack problem, but one of the most common is the 0-1 knapsack problem, which restricts the amount of times an item is selected to either zero or one. In this sense, it follows the real world analogy of an item being either selected and placed in the knapsack, or it being excluded from the knapsack and left out.

This can be defined thus [78]: let there be a set of items,  $z_1, z_2, \dots, z_i, \dots, z_n$  where  $z_i$  has a value  $v_i \in \mathbb{N}_+^*$  and a weight  $w_i \in \mathbb{N}_+^*$ .  $x_i$  is a boolean defining whether the item  $z_i$  is selected. The maximum weight of the selected items cannot exceed  $W \in \mathbb{N}_+^*$ .

$$\max \sum_{i=1}^{n} v_i x_i$$

(2.1) subject to:

$$\sum_{i=1}^{n} w_i x_i \le W,$$

$$x_i \in \{0, 1\}$$

This maximises the sum of the value of the selected items, whilst ensuring that the weight constraint, W, is not violated.  $x_i$  denotes how many times item i has been selected, and by altering the constraint applied to  $x_i$ , the problem can also be changed as required to reflect the real-world problem that is being mapped to it. For example, allowing x to be any value such that the constraint becomes  $x_i \ge 0$ , this allows as many copies of an item as required to be selected, and forms the *unbounded knapsack problem*. Similarly, if there is a different amount of each item available, the x constraint can be changed to  $x \in 0, 1, ..., c_i$ , where the amount of copies of each item  $(x_i)$  is restricted to a given limit,  $c_i$ . This is the *bounded knapsack problem*. An example instance of the knapsack problem is shown in Fig. 2.4, where the capacity of the knapsack is 18, and the maximum profit attainable from the item set is 49.

Due to the lack of a polynomial time algorithm that can assert for all cases whether or not a given solution to the problem is optimal, in terms of complexity the knapsack problem is *NP*-hard [78]. However, a reduction of the knapsack problem, referred to as the *decision*

Fig. 2.4 A knapsack instance where the subset of optimal items from a given set of input items is highlighted

*problem*, seeks to bound the problem and define whether or not a given profit value can be attained without exceeding the weight constraint, and this is *NP*-complete.

There exists dynamic programming algorithms that can solve the problem in pseudo-polynomial time, which will be the focus of this thesis and are introduced in Sec. 2.2. This dynamic programming algorithm runs in O(nW) time. Furthermore there has been a lot of focus on approximation methods - methods which seek to find a subset of solutions based on a reduced scaled version of the inputs. in an effort to then extrapolate to the real solution set. For the knapsack problem there are many approximation schemes which run in fully polynomial time. Finally, as with most optimisation problems, there exist many algorithms which seek to solve the problem inexactly through heuristic and meta-heuristic methods, which are briefly discussed in Sec. 2.3.1.

As the knapsack problem can be effectively represented as a simple linear integer program [45], higher level problems can be reduced to the knapsack problem, and it provides the

underpinnings of many decision and optimisation problems. Some of the most common uses are in work-flow scheduling or manufacturing, where an employee or a piece of machinery can be represented as a knapsack; in this instance, variations of the knapsack problem where there are multiple copies of an item become beneficial. It is also often used as a tool to analyse likely investments, where each has a specified return (the value of the knapsack item), but an initial cost (the weight of the knapsack item). The hardness of bigger instances of the problem also means that it can lend itself to supporting cryptographic systems [62].

## 2.1.4 Travelling Salesman Problem

The Travelling Salesman Problem (TSP) [7] is a classic NP-hard computer science problem. The goal of the problem is thus: given a set of vertices, construct a set of edges which connects all these vertices in an acyclic manner, where the cumulative length of the edges is sought to be minimised. The typical analogy given is a salesman travelling between a set of cities, who seeks to minimise the total driving distance.

This is formally defined, as given a set of vertices, which are cities, these are labelled 1,2,...,n. As aforementioned, each one of these vertices must be visited once, and for it to be a valid tour, the route must start and end at the same point. The naive, brute force algorithm has a huge computational complexity of O(n!), making exact solving impossible for all but the smallest instances; however, it is at the core of many vehicle routing and scheduling algorithms. To represent the construction of the route, let us define a variable x where for an n city problem  $x_{ij}$  is defined as:

$$x_{ij} = \begin{cases} 1 & \text{the route goes from city } i \text{ to city } j \\ 0 & \text{o.w.} \end{cases}$$

Let the cost of moving between two cities i and j be defined as  $c_{i,j}$ . Then with the use of a temporary variable,  $u_i$  Miller [63] shows how this problem can be defined as an integer linear program:

$$\min \sum_{i=0}^{n} \sum_{j \neq i, j=0}^{n} c_{ij} x_{ij}$$

(2.2)

subject to:

$$0 \le x_{ij} \in \{0, 1\} \le 1$$

$i, j = 0, ..., n$  (2.3)

$$u_i \in \mathbb{Z} i = 0, ..., n (2.4)$$

$$\sum_{i=0, i \neq j}^{n} x_{ij} = 1 \qquad j = 0, ..., n$$

(2.5)

$$\sum_{j=0, j\neq i}^{n} x_{ij} = 1 \qquad i = 0, ..., n$$

(2.6)

$$u_i - u_j + nx_{ij} \le n - 1$$

$1 \le i \ne j \le n$  (2.7)

Constraints 2.3 and 2.4 ensure that each city on the tour can only be arrived at from exactly one other city. Equalities 2.5 and 2.6 requires that from each city on the tour, there is a departure to exactly one other city. Finally, constraint 2.7 ensures that there is only a single tour covering all cities, and that there cannot be multiple, simultaneous disjointed tours.

There exists a dynamic programming based algorithm to solve this, called the Held and Karp algorithm, which will be discussed in Sec. 2.2; it reduces the computational complexity to  $O(2^n n^2)$ , with an associated memory complexity of  $O(2^n)$ . However, this is obviously still too high for most real world sized instances to be solved in a reasonable amount of time. Due to this, the problem is very rarely solved using exact methods and therefore, this problem is solved almost exclusively through inexact methods such as heuristics. A brief introduction to inexact methods is provided in in Sec. 2.3.1.

Fig. 2.5 A Manhattan tourist problem instance. The number of landmarks on each street denoted as the weight of the edges, the optimal solution is highlighted in the figure

## 2.1.5 Manhattan Tourist Problem

The aim of the Manhattan toursit problem is to find a route that crosses the borough of Manhattan, such that the amount of landmarks visited on the route is maximised. More generally each edge is assigned a weight, proportional to the number of landmarks on the edge, and the goal is to travel from a start vertex to a goal vertex maximising the total weight of the edges traversed. An example of this is shown in Fig. 2.5.

Within the Manhattan tourist problem the possible moves at each vertex is *south* or *east* to prevent cycles forming in the graph. Therefore it should be apparent that this problem is similar to the travelling salesman problem, with a different set of constraints; the goal is to traverse from A to B, whilst maximising the edge weight (rather than minimising distance in the case of the TSP), and there is no constraint to visit each node. Unlike the travelling salesman problem, this problem is not NP-hard.

This generalised *toy* problem can form the basis of more advanced problems; it shares the same foundation as the longest common subsequence problem, or the edit distance problem, whilst also being similar in its use case to the travelling salesman problem. Parallelising this problem is therefore beneficial, as demonstrating a model that can solve this simplistic case can have implications in solving more specific problems, and can likely also be used to solve other problems with minimal adaptation.

A naïve recursive algorithm to solve this problem would run in exponential time. Therefore there are dynamic programming solutions available to this problem [49], which are similar to those available for both the longest common subsequence problem [43] as well as the edit distance problem; again these will be discussed in Sec. 2.2. The complexity of such algorithms is dictated by the x and y dimensions of the input grid being considered, and therefore the computational complexity of the algorithm is O(xy).

## 2.1.6 All Pairs, Shortest Path Problem

The all pairs shortest path problem is a generalisation of the previously introduced Manhattan Distance Problem. It is concerned with finding the shortest routes through a directed acyclic graph using every combination of pairs of nodes in the graph as a start and end vertex.

The shortest path problem is defined as:

$$\min \sum_{ij \in A} w_{ij} x_{ij} \tag{2.8}$$

subject to:  $x \ge 0$

$$\forall i \sum_{j} x_{ij} - \sum_{j} x_{ji} = \begin{cases} 1 & i = s \\ -1 & i = t \\ 0 & o.w. \end{cases}$$

Fig. 2.6 A directed graph with the cost shown for traversing each edge, highlighting the shortest path from A to F.

A graphical representation of a small example of the shortest path problem is presented in Fig. 2.6.

In this notation, s is representing the source node, t the target node and  $w_{ij}$  is the cost of traversing the edge from i to j.  $x_{ij}$  is used as an indicator to denote whether or not the edge is present in the shortest path. From this definition, the problem moves to an all pairs, shortest path problem working out the shortest path between s and t when s and t are set to all pairs of nodes in the graph.

This is represented as an adjacency matrix, which is a matrix of size  $v \cdot v$  where each cell (i, j) of the matrix denotes the edge weight between node i and j, or  $\infty$  if there is no feasible path. In the case of the all pairs shortest path problem, once the algorithm has finished executing (i.e. the problem has been solved), the values in the adjacency matrix will be updated to reflect the shortest path between each i and j.

A brute force approach to solving this problem would obviously require considering every single edge between all the vertices of the graph, which would lead to the time complexity of  $O(v^2)$ . However, the method we seek to parallelise to solve this problem [29] is introduced in detail in Sec. 2.2.3.

As with the previous vehicle routing based problems, paralellisation is desirable as it allows larger matrix sizes to be computed, which may mean that entire route network can be calculated at once rather than having to break them down into smaller sub networks leading to efficiency savings.

# 2.2 Dynamic Programming

In this section the method of programming called *dynamic programming* is introduced, as it forms the use of dynamic programming based techniques the parallel model proposed in thesis is developed.

## 2.2.1 Definition

Dynamic programming allows large complex problems to be solved by breaking them down into smaller sub-problems, which are then solved independently, the results of which are combined to form the solution to the original problem [24].

The first property the problem must have is that it must be possible to break the problem down into *overlapping sub-problems* [22]. This means the results from the sub-problems are reused several times, or in a recursive situation the same problems are solved repeatedly, rather than creating a new problem every single time [19]. This is not to be confused with an approach such as divide and conquer, where the problem is broken down into to separate non-overlapping sub-problems which are then solved independently to reconstruct a solution.

The second property the problem is required to have is that it must have an optimal sub-structure. The best way to describe this is through the example of solving an optimisation problem starting from a time period t and ending at time period T. It should be apparent that it is required to solve sub problems s starting at later date first (subject to t < s < T). This is a very basic example of an optimal sub-structure. Another illustrative example would be to minimise the cost of a set of alternatives; where the search space can be partitioned into smaller subsets, and each of these alternatives only belongs to a single subset. These can be

further reduced, until finding the minimal cost of each subset is trivial, and it is apparent that this also solves the original larger problem. This is an optimal sub-structure.

The concept of the optimal substructure in turn leads to the Bellman's Principle of Optimality [8] and the Bellman Equation [24], which is a necessary condition for optimality when using a dynamic programming based solving method. This equation shows that a dynamic programming algorithm to solve an optimisation problem can be solved through recursion by defining the relationship between the the *score* or *value* of the optimisation at one period of time, and the change in this at the next period of time. This relationship is called the Bellman Equation, which we now define.

Let a state of the problem at time t be called  $x_t$ , therefore the initial state of the problem will be called  $x_0$ . The set of possible actions at each time step,  $a_t \in \Gamma(x_t)$ , is dependent on the current state, where  $a_t$  is the set of variables a that can be altered at this specific time step t. The transition from a state x due to the variables of a we represent as  $T(x_t, a_t)$ , and the value or score of  $T(x_t, a_t)$  we define as  $F(x_t, a_t)$ . Therefore the decision problem that requires optimisation can be defined as:

$$V(x_0) = \max_{\{a_t\}_{t=0}^{\infty}} \sum_{t=0}^{\infty} \beta F(x_t, a_t)$$

subject to:  $a_t \in \Gamma(x_t)$

$$x_{t+1} = T(x_t, a_t)$$

$$\forall t \in \{0, 1, \dots, \infty\}$$

$$0 < \beta < 1$$

$$(2.9)$$

In this notation  $V(x_0)$  is the value functions, and this is dependent on the initial state as the overall solution to the problem is dependent on all states following the initial state.

29

Breaking this problem down into smaller sub problems, which is the basis of dynamic programming is addressed by Bellman as:

"An optimal policy has the property that whatever the initial state and initial decision are, the remaining decisions must constitute an optimal policy with regard to the state resulting from the first decision." [8]

When a problem exhibits this structure, it means that is displays an optimal sub-structure, and as such is a suitable candidate for solving through dynamic programming. To mathematically represent the principle of optimality it is a case of considering the current time step separately to all future time steps, and then starting again for the next time step, as this new state will affect the whole future decision process. This can be represented as a recursive definition:

$$V\left(x_{0}\right)=max_{a_{0}}\left\{ F\left(x_{0},a_{0}\right)+\beta V\left(x_{1}\right)\right\} \tag{2.10}$$

subject to:  $a_{0}\in\Gamma\left(x_{0}\right)$

$$x_{1}=T\left(x_{0},a_{0}\right)$$

which we can simplify further to:

$$V(x) = \max_{a \in T(x)} \{ F(x, a) + \beta V(T(x, a)) \}$$

(2.11)

This recursive relationship can be identified in all of the following dynamic programming solving methodologies of the introduced problems.

# 2.2.2 Dynamic Programming Methods

In computer science, implementing a dynamic programming based algorithm is either done through simple recursion to directly reflect the mathematical representation, or memoization which allows the partial solutions to be stored in a table or similar data structure.

In the case of large problem instances, most languages would very quickly hit a recursion limit, where the call stack becomes full and the function cannot recurse further. Therefore using memoization this limitation can be removed; by storing partial solutions in main system memory, future function calls simply lookup this value then continue the calculation. Memoization can also be referred to as tabling.

Tabling allows us to break a problem down into sub-problems and, when we solve a new sub-problem, consult the scoring table to see if it has already been solved. If it has, the stored solution is loaded, if it has not then the solution to the sub-problem is calculated and stored in the table. This saves computation, at the expense of storage. Finally, this scoring table can then be traversed to find the solution to the overall problem.

# 2.2.3 Solving Problems Through Dynamic Programming

All of the solving methodologies used in this thesis assume that memoization is being used, and the (i, j) values in the following definitions show the location in the look-up table the partial solutions are to be stored.

### **Longest Common Subsequence Problem**

Assuming the characters of the first input string (A) are indexed  $A_1, A_2, A_i, \ldots, A_n$ , and the characters of the second input string (B) are indexed  $B_1, B_2, B_i, \ldots, B_m$ .

To identify the length of the longest common subsequence between the two strings a table is created which is of dimension  $m \cdot n$ , where n is the length of the first input string, and m is the length of the second. Each cell in the table  $m \cdot n$  contains an integer value denoting

the longest possible sub-sequence based on the sub strings from  $A_0, ..., A_i$  and  $B_0, ..., B_j$ . Therefore it should be apparent that the cell of the table (m,n) will contain the length of the longest common subsequence for the complete two sequences. This is defined in Eqn. 2.12, where LCS denotes the longest common subsequence scoring grid.

$$LCS_{i,j} = \begin{cases} \emptyset & i = 0 \text{ or } j = 0 \\ LCS_{i-1,j-1} + 1 & A_i = B_j \\ \max \begin{cases} LCS_{i-1,j} & o.w. \\ LCS_{i,j-1} \end{cases} \end{cases}$$

(2.12)

A dynamic programming based algorithm will work through populating this table beginning at (1,1) and moving through the table filling a row at a time. If the character of string A at location i matches the character of string B at location j, the running total of 'subsequence recorded so far', based on the previous count stored at i-1 and j-1, is incremented and updated [94]. In this manner the table can be filled using solutions to previous problems, satisfying the dynamic programming requirement of overlapping sub-problems. This approach is a bottom up method of dynamic programming.

Once the table has been filled, as well as having the length of the longest possible subsequence, it is also possible to trace back through the table to rebuild the actual sequence of characters. This is due to the fact it is possible to identify which characters are present in the subsequence, as it is on these characters that the count was updated. Therefore by beginning in cell (m,n) and tracing back to each point the count was incremented the longest common subsequence can be built, or if there are multiple LCS's of the same length, a single one of these will be produced. The definition of this is Eqn. 2.13, where LCSSTR denotes the scoring grid with the output from the longest common subsequence algorithm. With adaptation this relationship can be altered to produce many sub-sequences if there is more than one, but this is not discussed here.

$$LCSSTR_{i,j} = \begin{cases} "" & i = 0 \text{ or } j = 0 \\ LCSSTR_{i-1,j-1} \cdot a_i & x_i = y_j \\ LCSSTR_{i,j-1} & LCS_{i,j-1} > LCS_{i-1,j} \\ LCSSTR_{i-1,j-1} & o.w. \end{cases}$$

(2.13)

#### **Edit Distance Problem**

The edit distance problem can be solved using a similar procedure to the methodology presented for the longest common subsequence problem, as they are closely related.

$$d_{i0} = \sum_{k=1}^{i} w_{del}(b_k)$$

$$d_{0j} = \sum_{k=1}^{j} w_{ins}(a_k)$$

$$d_{ij} = \begin{cases} d_{i-1,j-1} & a_j = b_i \\ d_{i-1,j} + w_{del}(b_i) \\ d_{i,j-1} + w_{ins}(a_j) & a_j \neq b_i \\ d_{i-1,j-1} + w_{sub}(a_j, b_i) \end{cases}$$

(2.14)